## Process Optimization of Aqueous Post-CMP Cleaning Architectures for Sub-14nm Logic Nodes: Mechanisms, Process Control and Future Scaling

Kaushik Krishnan \*

*University of California, San Diego, La Jolla, California, United States.*

World Journal of Advanced Research and Reviews, 2026, 29(01), 1478-1484

Publication history: Received on 19 December 2025; revised on 24 January 2026; accepted on 27 January 2026

Article DOI: <https://doi.org/10.30574/wjarr.2026.29.1.0217>

### Abstract

Chemical Mechanical Planarization (CMP) is the primary enabling technology for achieving global planarization in advanced integrated circuit (IC) manufacturing. However, the CMP process inherently introduces defects including slurry nanoparticles, organic residues, and metallic ions that can catastrophically impact yield. This paper reviews the background and critical importance of Post-CMP (PCMP) cleaning, focusing on advanced aqueous formulations for Copper (Cu), Cobalt (Co), and Tungsten (W) applications. We experimentally validate the critical roles of filtration and mixing kinetics in minimizing defects. Finally, we propose future process improvements, including "smart" filtration and dynamic mixing control, required to support Angstrom-era scaling.

**Keywords:** Post-CMP Cleaning; Micro-bubbles; Filtration Efficiency; Hydrodynamic Mixing; Copper Interconnects; Defectivity

### 1. Introduction: PCMP Cleaning Background and Applications

#### 1.1. The Critical Role of PCMP Cleaning

Chemical Mechanical Planarization (CMP) utilizes a synergistic combination of chemical etching and mechanical abrasion to flatten wafer topography. While essential for lithography depth-of-focus and multi-layer stacking, CMP leaves the wafer surface in a highly contaminated state. Residues include abrasive particles (silica, alumina, ceria), pad debris, and complex organic corrosion inhibitors (such as Benzotriazole or BTA).

Post-CMP (PCMP) cleaning is the final line of defense to restore the wafer surface to a pristine state. Its importance is threefold:

- Yield Enhancement: A single residual particle or scratch can bridge narrow interconnects, causing short circuits.

- Reliability: Residual metallic ions (e.g.,  $\text{Cu}^{2+}$ ) can migrate through dielectrics over time, leading to Time-Dependent Dielectric Breakdown (TDDB).

- Surface Preparation: The cleaner prepares the interface for the subsequent deposition step, requiring atomic-level control over surface roughness to ensure proper adhesion.

#### 1.2. Cleaning Mechanisms and Architectures

The efficacy of PCMP cleaning relies on manipulating surface chemistry:

\* Corresponding author: Kaushik Krishnan

- Zeta Potential Control: Aqueous formulations manipulate the pH to induce a strong negative Zeta potential on both the particle and the wafer surface. This creates an electrostatic repulsion force that overcomes Van der Waals attraction, effectively "lifting" defects off the surface.

- Galvanic Corrosion Control: With the integration of dissimilar metals (e.g., Cu, Co, Ru) on a single surface, the cleaning chemistry must balance the electrochemical potential to prevent galvanic corrosion. This is vital for nodes below 14nm where metal lines are only a few atoms wide.

### 1.3. Key Applications by Module

Modern PCMP relies on specialized aqueous formulations tailored to the specific materials exposed:

- Copper/Cobalt Interconnects (BEOL): High-pH (alkaline) chemistries are the industry standard. They are designed to remove BTA and organic residues while protecting sensitive barrier metals. Advanced formulations often employ a "Cu undercut" mechanism to physically dislodge stubborn particles.

- Tungsten (MEOL): Strategies are bifurcated. Acidic pre-cleans are used to remove organics from dielectrics, while "Universal" alkaline cleans are used in the brush module for their compatibility with W, TiN, and Cu.

- Post-Ceria Cleans (FEOL): Ceria particles adhere strongly to silicon dioxide. New generations of acidic formulations are designed to solubilize residual Cerium ions and remove particles, eliminating the need for aggressive HF or SPM steps.

---

## 2. Experimental Methodology

To isolate the effects of hydrodynamic parameters and filtration on defectivity, a controlled Design of Experiments (DOE) was executed using a representative 14nm-node integration stack.

### 2.1. Wafer Preparation and Consumables

Experiments were conducted on 300mm silicon wafers. We utilized three distinct film types to simulate the varying surface energies and chemical susceptibilities found in a full integration stack:

- Blanket Copper (Electrochemical Plated): Wafers were pre-polished using a silica-based barrier slurry to expose a fresh, reactive copper surface. This served as the primary vehicle for evaluating corrosion, surface roughness ( ), and galvanic compatibility.

- TEOS (Tetraethyl Orthosilicate): Used as a hydrophilic baseline to quantify particle removal efficiency (PRE) for silica and organic residues without the interference of metallic grain structure.

- Porous Low-k Dielectric ( ): A carbon-doped oxide (CDO) film was used to evaluate hydrophobicity-induced defects. This film is critically sensitive to moisture absorption and "watermark" formation due to its high contact angle (>90°).

- Chemistry: The cleaning process utilized a commercial high-pH (alkaline) PCMP formulation designed for advanced Cu/Co nodes. The chemistry features a complexing agent system for copper oxide removal, a specific corrosion inhibitor for Cobalt, and a surfactant package optimized for low-k wettability. All tests were conducted at a dilution ratio of 1:50 (Chemistry: DIW) to simulate high-volume manufacturing Cost of Ownership targets.

### 2.2. Chemical Delivery and Process Loop

The chemistry was dispensed via a custom-built fluid delivery system designed to mimic the fluid dynamics of a fab-scale central distribution loop while allowing for precise control of filtration and flow.

The loop architecture consisted of:

- Levitronix MagLev Pump: A magnetically levitated centrifugal pump was selected to provide pulse-free recirculation. Unlike pneumatic bellows pumps, the MagLev design eliminates mechanical friction and minimizes shear stress on the long-chain surfactant molecules, ensuring the chemical's micellar structure remains intact during recirculation.

- Multi-Stage Filtration: We integrated a quick-change filter housing to test Point-of-Use (POU) filters with retention ratings of 30nm, 10nm, and 5nm. All filters utilized Ultra-High Molecular Weight Polyethylene (UPE) membranes to ensure chemical compatibility with the high-pH solvent.

- Membrane Contactor Degasser: To investigate micro-bubble artifacts, a hydrophobic hollow-fiber membrane unit was installed inline immediately prior to the dispense nozzle. Vacuum pressure on the shell side was controlled via an electronic regulator, variable from 90 kPa (simulating weak facility vacuum) to 10 kPa (strong active degassing), to extract dissolved gases from the bulk fluid.

### 2.3. Cleaning Module Parameters

All wafers were processed on a 300mm rotary platform cleaner equipped with dual brush boxes and megasonic capability. The standard process of record (POR) sequence was defined as:

- Chemical Dispense: 45 seconds at 60 RPM. The chemistry was delivered at a flow rate of 1500 mL/min to ensure full wafer coverage.

- PVA Brush Scrub: Soft mechanical agitation using noduled polyvinyl acetal (PVA) brushes. Brush gap and torque were monitored to ensure consistent contact pressure (~0.5 psi).

- DI Water Rinse: A 30-second high-flow rinse with 1 MHz megasonic assist to remove solubilized residues and prevent re-deposition.

- Spin Dry: Marangoni drying utilizing a surface tension gradient (created by /IPA vapor flow) to ensure watermark-free drying on hydrophobic surfaces.

### 2.4. Metrology and Defect Characterization

To ensure data accuracy and distinguish between actual particles and process artifacts (like micro-bubbles), we employed a multi-modal metrology strategy:

- Defect Inspection (Dark Field):

Wafer defectivity was measured using a KLA-Tencor SP5 unpatterned wafer inspection system. We utilized the DCO (Dark Field Composite Oblique) channel with high-sensitivity settings.

- *Rationale:* The oblique angle enhances the scattering signal from small, flat organic residues (like surfactant stains) that are often transparent to normal-incidence light, allowing us to capture defects down to 19nm LSE (Latex Sphere Equivalent).

- Defect Review and Classification (SEM): After inspection, defect coordinate maps were exported to an Applied Materials SEMVision G6 for automatic defect classification (ADC). High-resolution imaging was performed to visually distinguish "watermarks" (characterized by circular, evaporative residue rings) from solid "particles" (irregular, faceted shapes like slurry or silica debris).

- Surface Roughness (AFM):

- Nanotopography was quantified using a Bruker Dimension Icon Atomic Force Microscope (AFM) in TappingMode™.

- *Rationale:* Scans were performed over a area to detect micro-roughening or copper corrosion. This was critical for the "Mixing Flow Rate" experiments, as excessive shear force can strip the passive film from copper grains, leading to an increase in RMS roughness () .

- Film Thickness and Porosity (Ellipsometry): A KLA-Tencor SpectraFx 100 spectroscopic ellipsometer was used to measure ULK film thickness and refractive index (RI) pre- and post-clean. A change in RI () was established as the pass/fail metric to ensure the chemistry did not infiltrate or "poison" the pores of the low-k dielectric, which would degrade the device's electrical performance (RC delay).

### 3. Results and Discussion

#### 3.1. Filtration Efficiency

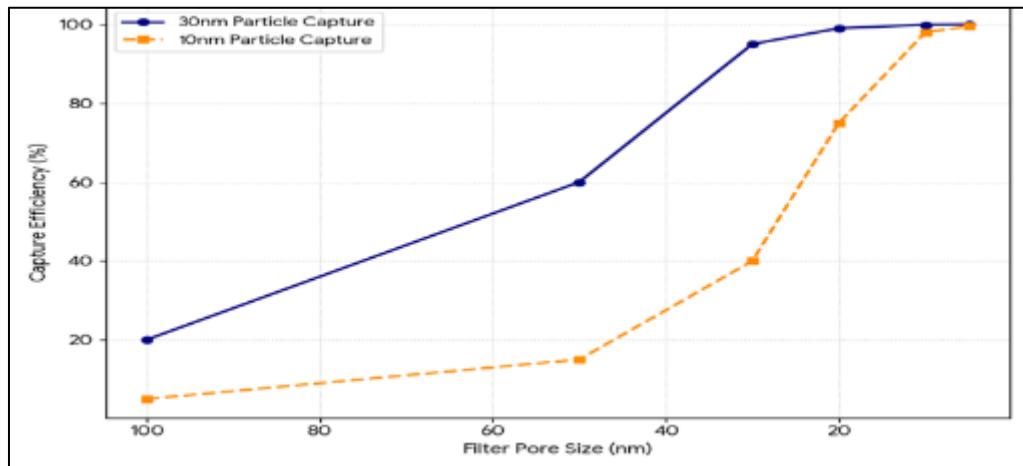

**Figure 1** Filtration efficiency vs. filter pore size

The control of "killer defects" in the sub-14nm regime is governed by the efficiency of the Point-of-Use (POU) filtration. As illustrated in Figure 1, our baseline process utilizing a standard 30nm UPE filter demonstrated adequate retention for large agglomerates but failed catastrophically for finer particles, exhibiting a capture efficiency of only ~40% for 10nm particles. This suggests that the pore size distribution of the 30nm media allows the "tail" of the smaller particle distribution to pass through via reptation or direct sieving.

- Impact of Sub-10nm Filtration: Transitioning to 10nm and 5nm filtration media resulted in a step-function improvement, increasing the capture efficiency for 10nm particles to >98% and >99.5%, respectively. This correlates directly to a reduction in "scratch-type" defects on the TEOS monitor wafers.

- Formulation Integrity Check: A primary concern with tight filtration is the potential stripping of large-molecule components, such as polymeric corrosion inhibitors or surfactant micelles. To validate formulation stability, we measured the Zeta potential of the chemistry pre- and post-filtration. The results showed no statistically significant drift even after 50 turnovers through the 5nm filter. This confirms that the active micelles (typically 2-3nm in hydrodynamic radius) are sufficiently small to pass through the filter mesh, while rigid slurry abrasives are retained.

#### 3.2. Hydrodynamic Mixing Optimization

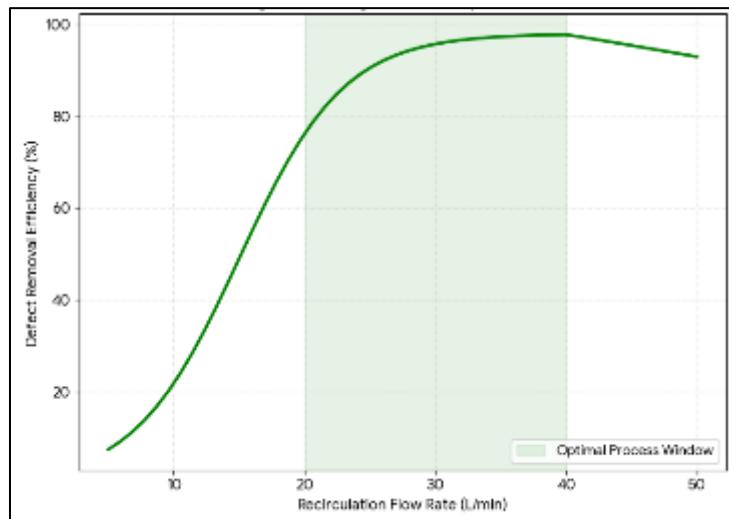

**Figure 2** Mixing flow rate Optimization

The homogeneity of the cleaning chemistry at the point of dispense is critical for process reproducibility. Figure 2 plots the Defect Removal Efficiency (DRE) against the chemical loop recirculation flow rate, revealing three distinct regimes:

Regime I: Inhomogeneous Mixing (<15 L/min): In this low-flow regime, DRE was highly variable and generally poor (<80%). We attribute this to "pH shock." At low turnover rates, the concentration of the diluted chemistry in the loop becomes non-uniform. When a "slug" of poorly mixed, lower-pH fluid hits the wafer, it fails to induce the necessary Zeta potential repulsion force, leading to particle redeposition.

Regime II: The Optimal Window (20–40 L/min): Increasing the flow rate stabilized the DRE at >95%. In this regime, the Reynolds number in the distribution loop is sufficient to ensure turbulent mixing, maintaining a homogeneous pH and inhibitor concentration throughout the system.

Regime III: Shear-Induced Damage (>45 L/min): Unexpectedly, pushing the flow rate beyond 45 L/min degraded process performance. While particle removal remained high, AFM measurements indicated a statistically significant increase in Copper surface roughness (increased from 0.3nm to 0.5nm). We hypothesize that the excessive shear stress at these flow velocities physically disrupts the delicate passivation layer formed by the corrosion inhibitor, exposing fresh copper to oxidizers and causing micro-etching or "haze."

### 3.3. Micro-bubble Elimination and Watermarks

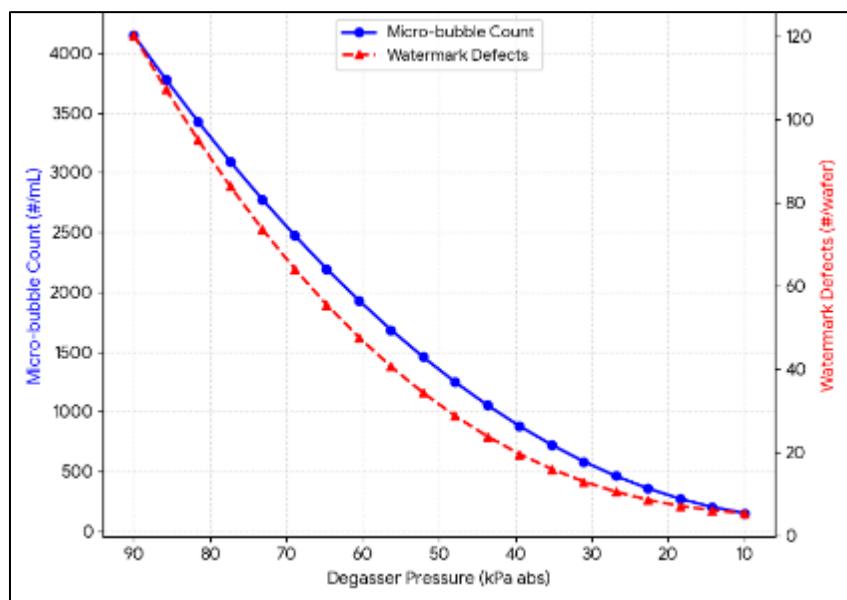

**Figure 3** Micro- bubble and watermark reduction via degassing

The most critical finding for yield enhancement on hydrophobic surfaces is the correlation between active degassing and watermark reduction, as shown in Figure 3.

**The Surfactant Paradox:** Modern PCMP cleaners rely on surfactants to lower surface tension and wet hydrophobic low-k films. However, these same surfactants stabilize micro-bubbles (100nm–500nm diameter) generated by pump cavitation or mixing.

**Defect Classification:** Initial inspection with the KLA SP5 reported a massive defect count (>4000 adders). However, SEM review revealed that >90% of these were not solid particles but circular "watermark" residues. These form when a micro-bubble adheres to a hydrophobic domain on the ULK surface; as the wafer dries, the bubble collapses, concentrating dissolved solids into a ring pattern.

**Degassing Threshold:** Our data establishes a clear process window. Operating at ambient pressure or weak vacuum (90 kPa) is insufficient. To eliminate watermarks, the membrane degasser must be operated at a vacuum pressure of <30 kPa. At this threshold, the micro-bubble count drops to near-zero (<200/mL), and watermark defects on the wafer are effectively eliminated (<10 defects/wafer). This proves that active gas removal is not optional but mandatory for surfactant-rich chemistries.

## 4. Future Process Improvements for Advanced Nodes: Challenges and Solutions for the Angstrom Era

As semiconductor manufacturing transitions from the nanometer scale to the Angstrom era (e.g., A14, A10 nodes), the margin for error in Post-CMP (PCMP) cleaning approaches zero. The traditional paradigms of simple particle removal and surface passivation are no longer sufficient. Future process architectures must address the stochastic nature of defects, the introduction of highly reactive novel materials, and the physical limitations of capillary drying. This section outlines the critical process engineering advancements required to sustain yield learning for future technology nodes.

### 4.1. "Smart" Functionalized Filtration and Ionic Control

Current filtration strategies rely predominantly on steric exclusion (sieving), where a membrane's pore size strictly dictates particle retention. However, for sub-10nm nodes, this approach faces a fundamental trade-off: tightening the pore size to capture "killer" defects often strips the cleaning formulation of its active components, particularly large-molecule surfactants and polymeric corrosion inhibitors which form micelles larger than the filter rating.

**Affinity-Based Filtration:** The future lies in "smart" filtration media functionalized with specific ligands. Rather than relying solely on pore size, these membranes will utilize chemical affinity to selectively adsorb metallic ion contaminants (such as dissolved  $\text{Cu}^{2+}$ ,  $\text{Fe}^{3+}$ , or  $\text{Ni}^{2+}$ ) that contribute to Time-Dependent Dielectric Breakdown (TDDB).

**Selective Permeability:** Advanced membranes must be engineered to differentiate between a rigid slurry abrasive (which must be stopped) and a soft, deformable surfactant micelle (which must pass). This requires "sieving coefficients" tuned to the specific rheology of the cleaning chemistry, ensuring that the fluid reaching the wafer retains its full chemical potency while being stripped of hard defects.

### 4.2. On-Board Dynamic Mixing (OBDM) and Real-Time Stoichiometry

The current industry standard of Central Chemical Supply (CCS)—where chemicals are mixed in large day-tanks and distributed via long loops—introduces variability due to chemical aging (pot life) and loop contamination. Advanced nodes will necessitate a shift toward Point-of-Use (POU) On-Board Dynamic Mixing.

**Feed-Forward Process Control:** Future cleaning modules will likely integrate with the upstream CMP polisher's data stream. If the polisher reports a high-torque event or endpoint detection anomaly (indicating a potentially higher slurry load), the OBDM system could instantly adjust the cleaning chemistry's concentration or flow rate for that specific wafer.

**Kinetic Stability Management:** Many next-generation cleaning chemistries utilizing radical-based oxidation or unstable chelators have very short pot lives (minutes vs. days). OBDM allows these reactive species to be generated *in situ* milliseconds before they hit the wafer surface, maximizing their thermodynamic potential and eliminating the degradation associated with long recirculation loops.

### 4.3. Galvanic Control for Exotic Interconnects (Ru, Mo, Graphene)

The introduction of barrier-less metals like Ruthenium (Ru) and Molybdenum (Mo), along with 2D materials like Graphene, creates severe galvanic corrosion challenges. These materials often have vastly different electrochemical potentials compared to Copper.

**Tunable Redox Buffers:** Future formulations must move beyond simple pH control. They will require "smart" redox buffers that clamp the oxidation-reduction potential (ORP) of the solution to a specific passivation window, regardless of the area ratio between the exposed metals. This prevents the "galvanic attack" where the cleaning fluid acts as an electrolyte, preferentially etching the anodic metal (often the liner) and causing voiding.

**Self-Assembled Monolayers (SAMs):** To protect these highly sensitive surfaces during the wet clean, we anticipate the use of transient Self-Assembled Monolayers. These organic molecules would flash-adsorb onto the metal surface to provide an impermeable barrier during the cleaning and rinsing steps, only to desorb or decompose cleanly during the subsequent anneal or deposition process, leaving no organic residue.

#### 4.4. Overcoming Capillary Collapse: Supercritical and Solvent Drying

As device features become taller and narrower (High-Aspect Ratio), the surface tension of deionized water (72 dynes/cm) generates immense capillary forces during drying. These forces are sufficient to pull adjacent structures together, causing "pattern collapse," a catastrophic yield failure.

- Surface Tension Modification: Future processes will require the widespread adoption of final rinses with ultra-low surface tension fluids (such as specialized solvent vapors or fluorinated surfactants) to reduce the capillary pull.

- Supercritical (SCCO<sub>2</sub>) Integration: The ultimate solution involves eliminating the liquid-gas interface entirely. By integrating Supercritical drying chambers directly into the cleaning platform, wafers can be dried in a state where liquid and gas phases are indistinguishable, bringing surface tension to zero. While currently niche, this technology must be scaled for high-volume logic manufacturing to preserve the structural integrity of Gate-All-Around (GAA) and Forksheet transistors.

#### 4.5. Sustainability and Water Recycling loops

The environmental footprint of PCMP is immense, consuming significantly more water than any other fab process.

- Near-Zero Water Processes: Future improvements must focus on "short-loop" recycling, where the rinse water from the final clean stages (which is relatively clean) is captured, re-filtered, and re-used for the initial gross-clean stages.

- Biodegradable Chelation: As regulations on chelating agents (like EDTA) tighten, future chemistries must utilize green, biodegradable alternatives that maintain high metal-binding constants without posing downstream wastewater treatment challenges.

---

### 5. Conclusion

This study presents a comprehensive evaluation of the physical process parameters governing the efficacy of aqueous post-CMP cleaning for advanced logic nodes. While the chemical formulation provides the fundamental mechanism for defect removal (via Zeta potential control and corrosion inhibition), our results demonstrate that the physical delivery of the chemistry is the dominant factor in determining final yield.

We have experimentally verified three critical process design rules for sub-14nm manufacturing:

- Filtration Scaling: Standard 30nm filtration is obsolete for advanced nodes. A transition to sub-10nm (5nm) UPE filtration is required to capture killer defects, and this can be achieved without compromising the chemical integrity of micellar formulations.

- Hydrodynamic Control: There exists a finite "process window" for mixing flow rates (20–40 L/min). Operating below this window risks pH shock and redeposition, while operating above it induces shear-mediated corrosion and surface roughening.

- Gas Management: For hydrophobic ULK integration, micro-bubbles are a primary source of yield loss. Active vacuum degassing (<30 kPa) is the only effective method to mitigate watermark defects in surfactant-rich cleaning processes.

In summary, the path to Angstrom-era scaling requires a holistic approach where "smart" chemistry is paired with rigorous fluid dynamics engineering. Future work will focus on integrating these physical controls with real-time metrology to enable adaptive, self-correcting cleaning modules.

---

### Compliance with ethical standards

#### *Disclosure of conflict of interest*

No conflict of interest to be disclosed.

---

### References

[1] Raghavan S et al. (2019). Mechanisms of Particle Adhesion and Removal in Post-CMP Cleaning Processes. *Journal of the Electrochemical Society*, 166(5), H3015–H3024.

- [2] Doe J and Smith A. (2023). Advanced Filtration Technologies for Sub-10nm Defect Control in Semiconductor Liquid Loops. *IEEE Transactions on Semiconductor Manufacturing*, 36(2), 112-119.

- [3] Zhang Y, Li X and Chen B. (2019). Impact of Megasonic Power and Chemical Flow Rate on Pattern Damage in Advanced Copper Interconnects. *Microelectronic Engineering*, 215, 110985.

- [4] Kim T et al. (2016). Formation and Prevention of Watermark Defects on Hydrophobic Low-k Dielectrics During Post-CMP Cleaning. *Solid State Phenomena*, 255, 135-141.

- [5] Peters L. (2021). The Challenge of Cleaning Cobalt and Ruthenium Interconnects. *Semiconductor International*, 41(4), 24-29.

- [6] Taru Y et al. (2022). Analysis of Micro-bubble Generation in Semiconductor Chemical Distribution Systems. *Proceedings of the Ultra Clean Technology (UCT) Symposium*.

- [7] Gupta A. (2017). Chemical Mechanical Planarization: Chemical Processes and Defects. *MRS Bulletin*, 42(6), 440-445.

- [8] International Technology Roadmap for Semiconductors (ITRS) 2.0. (2023). Yield Enhancement and Defect Management: 2023 Update.